I designed a template for System-on-a-Chip (SOC) hardware modeling, using the

SystemC library.

I also wrote a utility library, that provides extra functionality for such simulations.

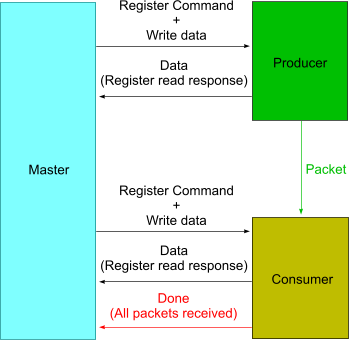

This is an example of an untimed simulation of 3 modules: Master, Producer and Consumer.

The Master programs the Producer to send a given number of packets to the Consumer, and the Consumer to expect that many packets from the Producer. Once the Consumer received the said packets, it sends a Done signal to the Master, which then either repeats the cycle or ends the simulation.

Small as it is, this example demonstrates:

1. The use of blocking events and blocking interfaces to control "hardware" modules.

2. The definition of memory addressable registers with the use of generic base classes for Register and Field, and

3. The control of debugging print-out messages via command line options and/or a simple text file.

I built this on Linux, using

non-recursive Makefiles, but any other building method and OS should work too.

I posted a description of this work, and a downloadable ZIP file with all the code on:

https://socmodeling.weebly.comI hope you find this useful!